News

一、什么是ADC的孔径延迟、它对ADC性能是否造成影响?

孔径延迟,英文释义为Aperture delay,是由于采样保持开关关断需要一定时间,相当于在采样时钟上引入一个小延迟,使得采集的信号为实际信号的延迟版本,因此,若孔径延迟是固定常数,则它并不产生误差,只会在时钟输入或模拟输入中起固定延迟的作用。

但若是两个AD转换器同步采样应用,由于不同AD转换器的孔径延迟是有差异的,可能给高摆率的信号带来误差,那么两个AD转换器必须精密匹配,必须适当调整采样时钟相对ADC的相位,从而消除孔径延迟不匹配问题。

二、什么是ADC的孔径抖动,它与孔径延迟一样吗?

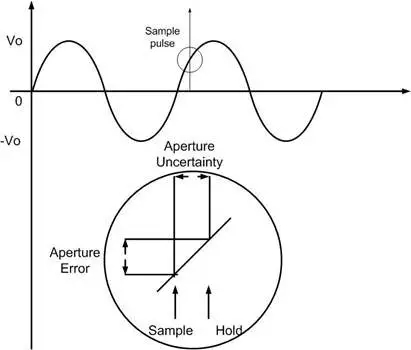

前文我们理解了孔径延迟,若其存在样本间变化(即,不同的输入信号带来不同的孔径延迟),则会产生电压误差,在开关断开时刻,这种样本间变化称为孔径抖动,英文释义为Aperture jitter,或叫孔径不确定性英文释义为Aperture uncertainty,如下图所示,从而带来孔径抖动误差(Aperture jitter error),用均方根皮秒(ps rms)来衡量。

图1 孔径抖动

三、孔径抖动对ADC信噪比的影响

下面仅单独考虑孔径抖动对ADC信噪比的影响。

假定对n位的ADC输入频率为f的满幅度正弦信号,表示为下式:

V(t)=V0*sin(2πft)

由于时钟抖动引起的SNR可以简述为下式:

SNRj=-20log2πftj

tj表示抖动时间的均方根。

可见,SNR随输入信号的频率减小,但与输入信号的幅度无关,可以简单计算一下,一个输入信号频率为f=24M的ADC,它的抖动时间造成SNR降低情况如下:

tj=0.5ps,SNRj=82.45dB

tj=1ps,SNRj=76.43dB

tj=3.48ps,SNRj=65.6dB

tj=5ps,SNRj=62.45dB

可以发现,SNR随孔径抖动时间增加下降很快,可知其带来的影响非常严重,尤其是在高速ADC应用中,其带来的信噪比衰减更快。

芯力特电子科技有限公司(简称芯力特公司)是一家专业从事混合信号集成电路设计的高科技企业,有专业的ADC设计团队,全面考虑各种非理想因素对ADC性能带来的影响,可以为客户定制性能优异、多种类型的ADC。公司围绕智慧电网等物联网致力于相关芯片技术攻关,采用灵活的商务模式提供专门的人力、物力进行技术服务与产品的定制设计,以满足客户的专用型需求,以一站式的服务达到客户与自身双赢的目的。

芯力特公司有非常优秀的AD/DA设计能力,在硅片上成功研发过多种AD,DA芯片与IP:

1)高精度高速10bit 100MHz pipeline/12bit 60MHz pipeline的ADC,已经在0.18um/0.13um CMOS工艺验证;

2)高精度低速低功耗12bit 4MHz SAR ADC,已经在0.18um CMOS工艺验证;

3)高精度低速的sigma-delta ADC,从14-24bit,已经在0.5um/0.35um/0.18um CMOS工艺验证;

4)极高速的200MHz 6-8bit flash ADC,已经在0.18um/0.13um CMOS工艺验证;

5) 8/10/12bitDAC,已经在0.35um/0.25um/0.18um/0.13umCMOS工艺验证。

联系方式:

联系人:张文杰

电话:18502537108

Email:zwj@sitcores.com

网址:www.sitcores.com

扫码二维码关注“芯力特”微信号

Address: Room 1401, Headquarters Building, Changsha Zhongdian Software Park, No. 39, Jianshan Road, Changsha Hi-tech Development Zone, Changsha City, Hunan Province

Shanghai: No.88, Shangke Road, Pudong District, Shanghai

Shenzhen: 24F IMT Tower, No,1 Gaoxin South Road 7th Avenue, Nanshan, Shenzhen

Service-Tel: 18684986553

Service: service@sitcores.com

Recruit: tinachen@sitcores.com

Copyright © 2020 Hunan Silicon Internet of Things Technology Co., Ltd 湘ICP备2022017381号